|

|

void adc_gpio_ain_init(void)

{

//设置杂项通道EN和ADC状态机状态cnt 2( 杂项通道的“设置”阶段和“捕获”状态)

adc_set_chn_enable_and_max_state_cnt(ADC_MISC_CHN, 2);//设置采样状态机和通道

的总长度 //设置杂项通道的“捕获状态”长度: 240

//设置杂项通道的“设置状态”长度: 10

//adc 状态机周期 = 24M/250 = 96K, T = 10.4 uS

#if (MCU_CORE_TYPE == MCU_CORE_8278)

adc_set_state_length(240,10);//设置 R_max_mc,R_max_c,R_max_s

#else

adc_set_state_length(240, 0, 10);

#endif //设置杂项通道使用differential_mode(泰凌建议:只有差模可用)

//单模ADC源,PB4例如:PB4正通道,GND负通道

gpio_set_func(GPIO_PC4,AS_GPIO);

gpio_set_input_en(GPIO_PC4, 0);

gpio_set_output_en(GPIO_PC4, 0);

gpio_write(GPIO_PC4, 0);

#if(MCU_CORE_TYPE == MCU_CORE_827x)

adc_set_ain_channel_differential_mode(B4P, GND);

//设置杂项通道分辨率 14 bit

//注意:differential_mode MSB是符号位,其余是数据位,这里BIT(13)是符号位

adc_set_resolution(RES14);//设置分辨率

//设置杂项通道vref 1.2V

adc_set_ref_voltage(ADC_VREF_1P2V);//设置通道Vref

//设置杂项t_sample 6个adc clock周期: 6 *1/4M

adc_set_tsample_cycle(SAMPLING_CYCLES_6); //采样阶段

的ADC时钟周期数 #elif(MCU_CORE_TYPE == MCU_CORE_825x)

adc_set_ain_channel_differential_mode(ADC_MISC_CHN, C4P, GND);

//设置杂项通道分辨率 14 bit

//注意:differential_mode MSB是符号位,其余是数据位,这里BIT(13)是符号位

adc_set_resolution(ADC_MISC_CHN, RES14);//设置分辨率

//设置杂项通道Vref 1.2V

adc_set_ref_voltage(ADC_MISC_CHN, ADC_VREF_1P2V);//设置通道Vref

设置其他 t_sample ADC时钟周期 6 * 1/4M

adc_set_tsample_cycle(ADC_MISC_CHN, SAMPLING_CYCLES_6);//采样阶段

ADC时钟周期数 #endif

//设置模拟输入预分量 1/8

adc_set_ain_pre_scaler(ADC_PRESCALER_1F8);

}

void adc_gpio_ain_init_test(void)

{

//设置杂项通道EN和ADC状态机状态cnt 2(杂项通道的“设置”阶段和“捕获”状态)

adc_set_chn_enable_and_max_state_cnt(ADC_MISC_CHN, 2);//设置采样状态机和通道

的总长度 //设置“ca杂项通道的”设置状态“长度: 240

//设置杂项通道的”设置状态“长度: 10

//ADC状态机周期 = 24M/250 = 96K, T =10.4 uS

#if (MCU_CORE_TYPE == MCU_CORE_8278)

adc_set_state_length(240,10);//设置R_max_mc,R_max_c,R_max_s

#else

adc_set_state_length(240, 0, 10);

#endif //设置其他通道使用differential_mode(泰凌建议:只有差模可用)

//单模ADC源,PB4例如:PB4正通道,GND负通道

gpio_set_func(GPIO_PC5,AS_GPIO);

gpio_set_input_en(GPIO_PC5, 0);

gpio_set_output_en(GPIO_PC5, 0);

gpio_write(GPIO_PC5, 0);

#if(MCU_CORE_TYPE == MCU_CORE_827x)

adc_set_ain_channel_differential_mode(B4P, GND);

//设置杂项通道分辨率 14 bit

//注意:differential_mode MSB是符号位,其余是数据位,这里BIT(13)是符号位

adc_set_resolution(RES14);//设置分辨率

//设置杂项通道 vref 1.2V

adc_set_ref_voltage(ADC_VREF_1P2V);设置通道 VREF

设置其他 t_sample ADC 时钟周期:6 * 1/4M

adc_set_tsample_cycle(SAMPLING_CYCLES_6);采样阶段的 ADC 时钟周期数 #elif(MCU_CORE_TYPE == MCU_CORE_825x)

adc_set_ain_channel_differential_mode(ADC_MISC_CHN,C5P,GND);

将其他通道分辨率设置为 14 位

注意: differential_mode MSB 是符号位,其余是数据,其中 BIT(13) 是符号位

adc_set_resolution(ADC_MISC_CHN,RES14);设置分辨率

设置杂通道 VREF 1.2V

adc_set_ref_voltage(ADC_MISC_CHN, ADC_VREF_1P2V);设置通道 VREF

设置其他 t_sample ADC 时钟周期:6 * 1/4M

adc_set_tsample_cycle(ADC_MISC_CHN, SAMPLING_CYCLES_6);采样阶段

的 ADC 时钟周期数 #endif

将模拟输入预分频设置为 1/8

adc_set_ain_pre_scaler(ADC_PRESCALER_1F8);

使用

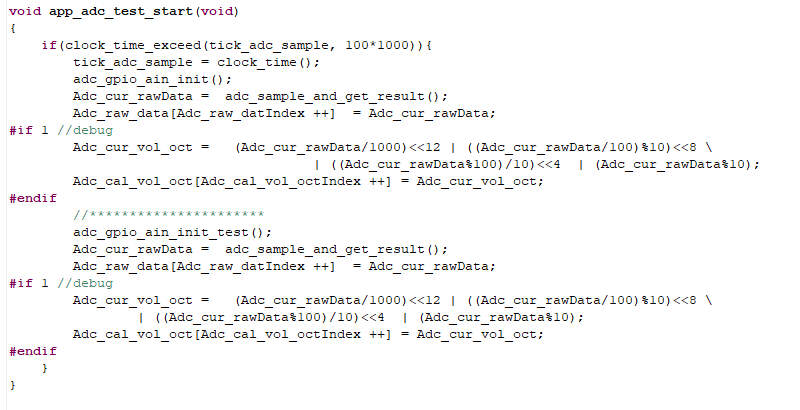

sdk 进行 b85m_driver_test/app_adc.c,在源码的基础上增加一个 ADC 采样的引脚,即同时取 C4/C5,断开硬件电路,交流块测量 C5 引脚会出现在图中的峰值杂散处。有没有解决方法

|

|

![]() 沪公网安备31011502403548号 )

沪公网安备31011502403548号 )